## 1 Worksheet 2: Plateauing the Counters

## 1.1 Aim

Before you use any detector you need to make sure that it is set up properly and working correctly. Otherwise, you cannot trust the data which you are recording. When you come to present your results, nobody will accept them unless you can show that the detector is working as expected. The aim of this worksheet is the find the optimum operating conditions for your detector. For this worksheet you will need a stopwatch.

## 1.2 The Control Voltage

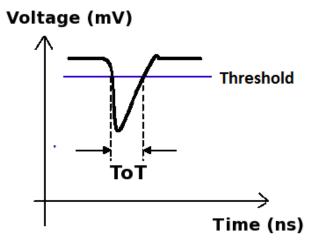

The aim of the Power Distribution Unit (PDU) is to apply a voltage across the photomultiplier tube, called the control voltage. The size of the signal produced by the PMT is determined by the control voltage, the higher the voltage, the larger the signals will be. Usually, signals which are produced when muons pass through the scintillator will be quite large. Signals which are produced by other sources tend to be smaller. Since we are not interested in these types of signals, they are usually called *noise*, and they get in the way of detecting the cosmic rays. We therefore want to ignore these small signals and only count large signals from muons. To do this, the DAQ board only accepts signals above a certain threshold, which is by default set to 300mV. Noise signals will usually be below this, and so will be ignored by the card. However, if the control voltage is set too low, then the signals produced by cosmic rays will be below the threshold, and so we will not detect every particle which passes through. Conversly, if the control voltage is too high then the noise signals will be above the threshold and so will be incorrectly counted as cosmic rays. At

the same time, operating at a high voltage puts a lot of strain on the PMTs, so to extend their lifetime we need to operate at the lowest voltage possible while still detecting as many cosmic rays as we can. To find this optimum control voltage we go through a process called "Plateauing the counters". The reason for calling it this will soon become apparent.

## 1.3 Finding the Plateau

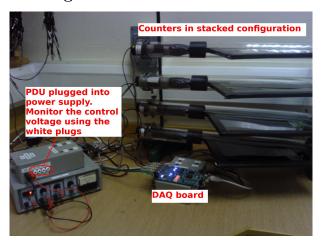

In order to plateau a counter, you need to set up the detector with 2 counters, one on top of the other. One will be the counter which you want to plateau, which we will call Counter 1, and the other will be your reference counter, which we will call Counter 2.

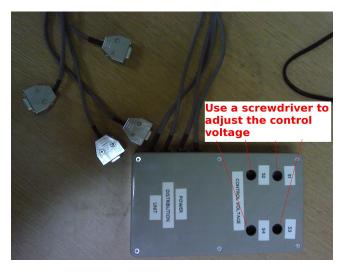

You can test the control voltage on each counter by plugging a digital multimeter (DMM) into the PDU across the 0V (black) and control voltage (white) plugs. Each counter has a separate plug for its control voltage. The control voltage can then be changed by turning the corresponding variable resistor in the PDU.

Follow the steps below to plateau the first counter:

- 1. Set the control voltage across Counter 2 to 1V.

- 2. Set the control voltage across Counter 1 to  $0.55\mathrm{V}$

- 3. Open up hyperterminal. Details of how to use hyperterminal can be found in the appendix to this pack. Type WC 00 13, which will set up the DAQ board to look for coincidences between the two counters.

- 4. Type TL 4 300 to set the threshold of all 4 counters to 300mV.

| Set   Concected 0000115   Auto detet:   115208-N-1    Serour   Pinteche   P   | qnet - HyperTerminal                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VI Node Channels which are enabled Ch(s) Enabled (1,0) Cad DC Reg CO using (bits 3-0) Veto Enable Ch(s) Enabled (1,0) Cad DC Reg CO using (bits 3-0) Veto Enable Ch(s) Coincidence Level (bits 7.6) Coincidence 1-6/2-Fold Coincidence Level (bits 5.4) Pipe Line Delay: 40 NS Cad DT Reg T1=rDelay Reg T2= Cate Width 100 NS Cad DT Reg T1=rDelay Reg T2= Cate Width 10.300 vlts Card DT Reg C2-LowByte Reg C3-HighByte 10nS/cnt  ChO Threshold 0.300 vlts Largest time between Ch1 Threshold 0.300 vlts Ch3 Threshold 0.300 vlts Test Pulser Vlt: 3.000 vlts Test Pulse Ena: Off  Example line for 1 of 4 channels. (Line Drawing, Not to Scale) Input Pulse Edge 'RE' Tag Bit Tag Bit Tag Bit Belayed Reg Edge 'RE' Tag Bit Tag Bit Edge 'FE' | File Edit View Call Transfer Help                                                                                                                                                                                                                                                                  |

| Run Mode : On Channels William are enabled shle) Ch(s) Enabled : Off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                    |

| Ch1 Threshold : 0.300 vlts  Ch2 Threshold : 0.300 vlts Ch3 Threshold : 0.300 vlts Lest Pulser Vlt: 3.000 vlts Lest Pulser Vlt: 3.000 vlts Lest Pulse Ena : Off  Example line for 1 of 4 channels. (Line Drawing, Not to Scale) Linput Pulse edges (begin/end) set rising/falling tags bits.  Input Pulse, Gate cycle begins Delayed Rise Edge 'RE' Tag Bit Delayed Rise Edge 'RE' Tag Bit Legte 'FE' Tag  | Run Mode : On Crannels Wnich are enabled able) Ch(s) Enabled : (1,0) Cmd DC Reg CO using (bits 3-0) Veto Enable : Off VE 0 (Off), VE 1 (On) Veto Select : Ch0 Coincidence Level (bits 7,6) Coincidence 1-4 2-Fold Coincidence Level (bits 5,4) Pipe Lipe Delaw: A0 nS Cmd DT Reg T1=FDelaw Reg T2= |

| Ch3 Threshold : 0.300 vlts Test Pulser Vlt: 3.000 vlts Test Pulse Ena: Off  Example line for 1 of 4 channels. (Line Drawing, Not to Scale) Input Pulse edges (begin/end) set rising/falling tags bits. Input Pulse, Gate cycle begins Delayed Rise Edge 'RE' Tag Bit Delayed Fall Edge 'FE' Tag Bit Iag Bits delayed by PipeLnDly PipeLineDelay : 40nS    Capture Window: 60nS   Gate Width : 100nS  If 'RE', 'FE' are outside Capture Window, data tag bit(s) will be missing. CaptureWindow = GateWidth - PipeLineDelay The default Pipe Line Delay is 40nS, default Gate Width is 100nS. Setup CMD sequence for Pipeline Delay. CD, WI 1 0, WI 2 nn (10nS/cnt) Setup CMD sequence for Gate Width. CD, WC 2 nn(10nS/cnt), WC 3 nn (2.56uS/cnt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                    |

| Input Pulse edges (begin/end) set rising/falling tags bits. Input Pulse, Gate cycle begins Delayed Rise Edge 'RE' Tag Bit Delayed Rise Edge 'R' Tag Bit Delayed Rise Edge 'RE' Tag Bit Delayed Rise Edge 'R' Tag Bit Delayed R | Ch3 Threshold : 0.300 vlts<br>  Test Pulser Vlt: 3.000 vlts                                                                                                                                                                                                                                        |

| Gate Width : 100nS   If 'RE','FE' are outside Capture Window, data tag bit(s) will be missing.   CaptureWindow = GateWidth - PipeLineDelay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input Pulse edges (begin/end) set rising/falling tags bits. Input Pulse, Gate cycle begins Delayed Rise Edge 'RE' Tag Bit Delayed Fall Edge 'FE' Tag Bit Belayed by Tag Bits delayed by PipelnDly                                                                                                  |

| If 'RE', 'FE' are outside Capture Window, data tag bit(s) will be missing. CaptureWindow = GateWidth - PipelineDelay The default Pipe Line Delay is 40nS, default Gate Width is 100nS. Setup CMD sequence for Pipeline Delay. CD, WT 1 0, WT 2 nn (10nS/cnt) Setup CMD sequence for Gate Width. CD, WC 2 nn(10nS/cnt), WC 3 nn (2.56uS/cnt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | III                                                                                                                                                                                                                                                                                                |

| CaptureWindow = GateWidth - PipeLineDelay The default Pipe Line Delay is 40nS, default Gate Width is 100nS. Setup CMD sequence for PipeLine Delay. CD, WT 1 0, WT 2 nn (10nS/cnt) Setup CMD sequence for Gate Width. CD, WC 2 nn(10nS/cnt), WC 3 nn (2.56uS/cnt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                    |

| Connected 00:01:15 Auto detect 115200 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CaptureWindow = GateWidth - PipeLineDelay<br>  The default Pipe Line Delay is 40nS, default Gate Width is 100nS.<br>  Setup CMD sequence for Pipeline Delay. CD. WT 1 0, WT 2 nn (10nS/cnt)                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Connected 00:01:15 Auto detect 115200 8-N-1 SCROLL CAPS NUM Capture Print echo                                                                                                                                                                                                                     |

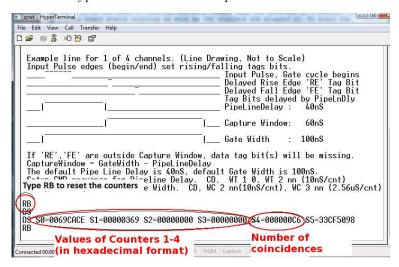

- 5. Type V1 to check that the last two commands worked.

- 6. We now need to find out how many cosmic rays are detected in a minute. The DAQ board starts counting as soon as the counters are plugged in. To start the counters again you can use the command RB. Type RB and start the stopwatch at the same time.

- 7. After one minute, type the command DS. This displays the counters on the board and tells you how many cosmic rays have been seen. The numbers are all in a hexadecimal format. The value of S4 is the number of coincidences, i.e. the number of comsic rays detected.

- 8. Type the value of the control voltage and the value of S4 into MS Excel. Use the hex2dec() function to convert the flux into a decimal number.

- 9. Increase the control voltage across Counter 1 to 0.6V and repeat the process to find out how many coincidences there are in a minute.

- 10. Repeat this until you reach a control voltage of 1.3V

- 11. Now use MS Excel to obtain a plot of counts per minute against control voltage.

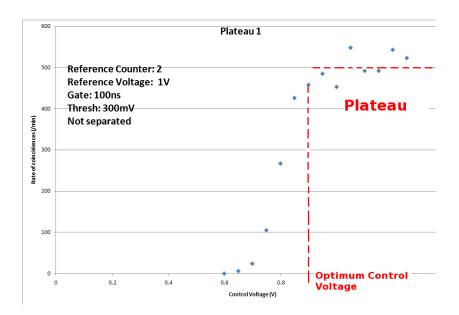

Your plot should look similar to the one above. There should be very few counts below a certain point, and when the control voltage is large enough that the signals are above the threshold, then the counts per minute should increase. The counts per minute should level off when all the cosmic rays are being detected. This levelling off is called the plateau. The operating voltage should be set to the voltage just above where the plateau begins.

You can now plateau the other counters using Counter 1 as a reference counter. Set the control voltage across Counter 1 to the optimum voltage found, and use it to plateau the other counters.